LCWS2019 (Sendai)

# SOFIST, an SOI based pixel sensor for the ILC

**SOFIST: SOI Fine measurement of Space and Time**

Kazuhiko Hara University of Tsukuba, Tomonaga Center for the History of the Universe

T. Tsuboyama, Y.Arai, I. Kurachi, S. Ono\*, Takayanagi, M. Togawa (KEK), K. Hara, S. Iwanami, H. Murayama (U. Tsukuba), M. Yamada (TMCIT), T. Li (Tohoku U.), M. Ikebe (Hokkaido U.), M. Motoyoshi (Tohoku Micro Tec Co., Ltd.), and the SOIPIX collaboration

\*now at SONY Co.Ltd

# **Vertexing at the ILC**

- Spatial resolution near the IP better than 3  $\mu m$

- Material budget below 0.15% X<sub>0</sub>/layer

- Low-power ASICs (~50mW/cm<sup>2</sup>)+gas-flow cooling

- The first layer located at a radius of  $\geq$  1.6 cm

- Pixel occupancy not exceeding a few %

- Radiation: TID<1kGy/y, NIEL<10<sup>11</sup> n/cm<sup>2</sup>/y

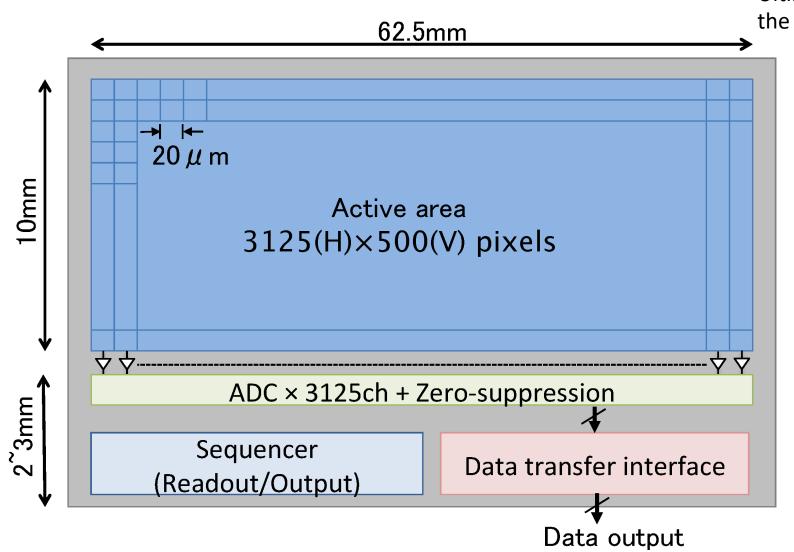

- We choose SOI monolithic, pixel size 20x20  $\mu\text{m}$

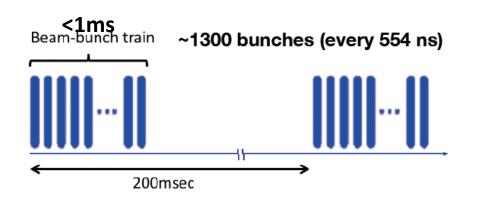

- store data during the train, readout them in between trains

- 3 memories each for the signal charge and arrival time

- ⇒ SOFIST (SOI fine measurements of space and time)

Occupancy /(20 $\mu$ m)<sup>2</sup>/train and the efficiencies (vs #memories) at the innermost layer

| E <sub>CM</sub> (GeV) | λ    | $\Sigma e^{-\lambda}(\lambda)^N/N!$ (%) |       |       |       |       |       |       |  |

|-----------------------|------|-----------------------------------------|-------|-------|-------|-------|-------|-------|--|

|                       |      | N=0                                     | 1     | 2     | 3     | 4     | 7     | 8     |  |

| 250                   | 0.09 | 91.42                                   | 99.62 | 99.99 | 100   | 100   | 100   | 100   |  |

| 350                   | 0.12 | 89.38                                   | 99.42 | 99.98 | 100   | 100   | 100   | 100   |  |

| 500                   | 0.20 | 81.95                                   | 98.26 | 99.89 | 99.99 | 100   | 100   | 100   |  |

| 1000                  | 2.04 | 13.00                                   | 39.52 | 66.58 | 84.98 | 94.36 | 99.88 | 99.97 |  |

numbers are scaled from study of Mori (Tohoku U, master thesis) made for  $(5\mu m)^2$  FPCCD, 2014, using Guinea Pig+Mokka

0.75x10<sup>34</sup>/cm<sup>2</sup>/s @0.25TeV? 1.8x10<sup>34</sup>/cm<sup>2</sup>/s @0.5TeV 3.6x10<sup>34</sup>/cm<sup>2</sup>/s @1 TeV

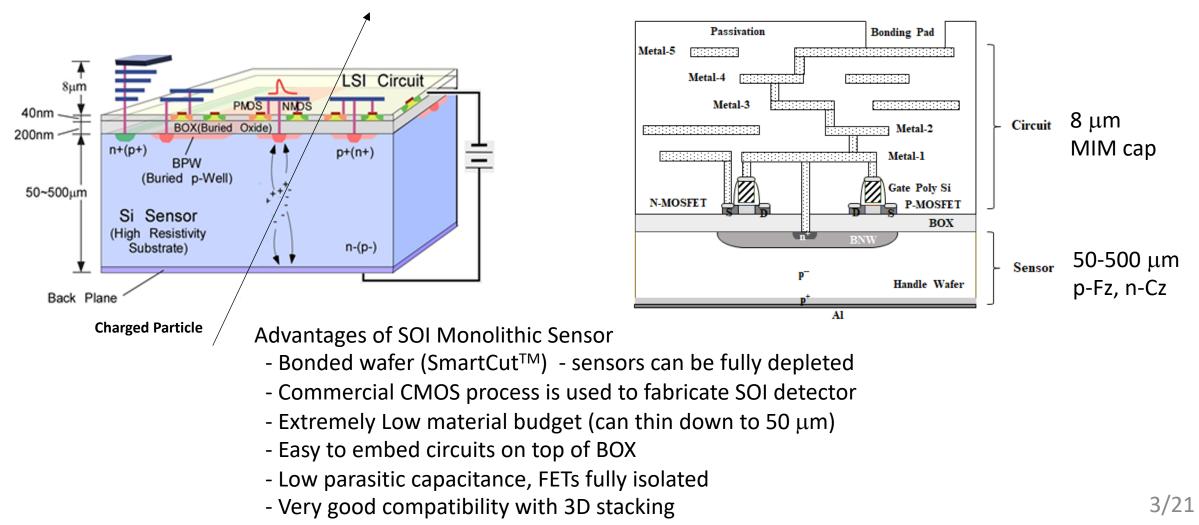

### **SOI monolithic sensor**

Monolithic sensor using silicon-on-insulator (SOI) technology: Lapis 0.20µm FD-SOI Pixel nodes (in handle Si) are electrically connected to readout circuit (SOI layer) through small vias fabricated in a conventional LSI process.

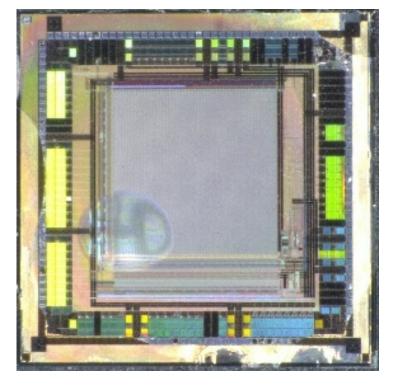

# **SOFIST layout**

Ultimate layout to fit in the ILD vertex geometry

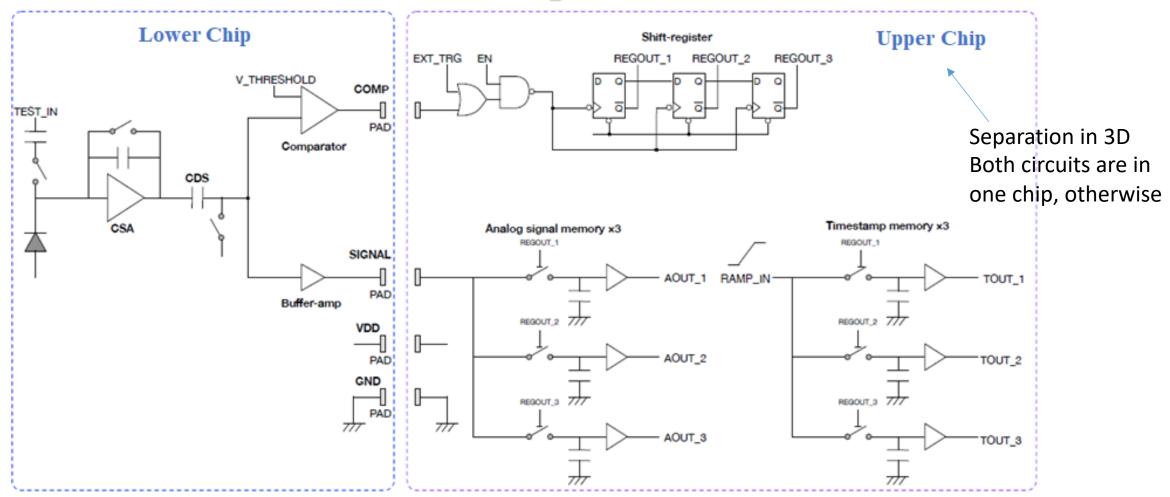

### **SOFIST on-pixel circuit**

Multiple memories: dead-time less data store possible

Timestamp data: distinguish hits associating to individual events

- separation of beam bunches (554ns) is ideal, but separation O(1us) would help a lot Readout all memory data (charge and time) in a column by one ADC

# **SOFIST in development**

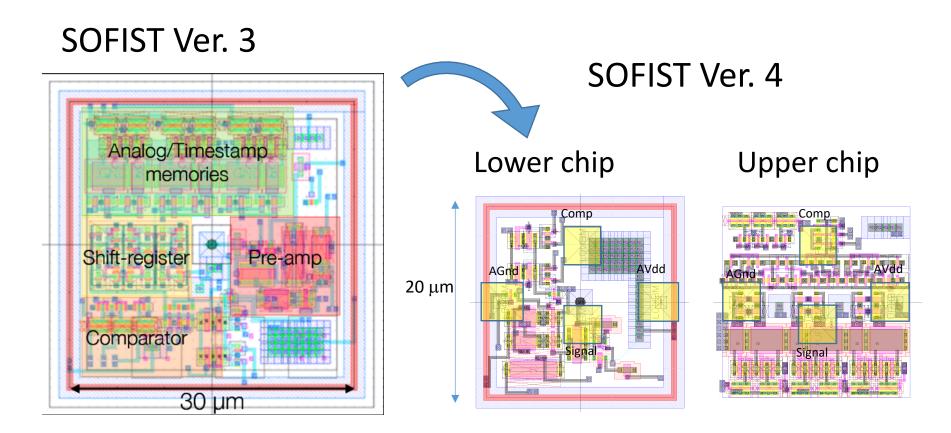

| Ver. 1                | Ver. 2                                                         | Ver. 3                                                                                                                 | Ver. 4                                                                                                                                                                                                      |

|-----------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2016/2017             | 2017/2018                                                      | 2018/2019                                                                                                              | 2018/2020                                                                                                                                                                                                   |

| SOI                   | DSOI                                                           | DSOI                                                                                                                   | DSOI                                                                                                                                                                                                        |

| 20x20                 | 25x25                                                          | 30x30                                                                                                                  | 20x20                                                                                                                                                                                                       |

| 2                     | 0                                                              | 3                                                                                                                      | 3                                                                                                                                                                                                           |

| 0                     | 2                                                              | 3                                                                                                                      | 3                                                                                                                                                                                                           |

| 3x3x500               | 4.5x4.5x75                                                     | 6x6x300                                                                                                                | 4.5x4.5x300                                                                                                                                                                                                 |

| Spatial<br>column ADC | Time<br>column ADC                                             | Both<br>column ADC                                                                                                     | Both**<br>column ADC<br>3D                                                                                                                                                                                  |

|                       | 2016/2017<br>SOI<br>20x20<br>2<br>2<br>0<br>3x3x500<br>Spatial | 2016/2017   2017/2018     SOI   DSOI     20x20   25x25     2   0     0   2     3x3x500   4.5x4.5x75     Spatial   Time | 2016/2017   2017/2018   2018/2019     SOI   DSOI   DSOI     20x20   25x25   30x30     2   0   3     0   2   3     3x3x500   4.5x4.5x75   6x6x300     Spatial column ADC   Time column ADC   Both column ADC |

\* Yearly test beam activities at FNAL This year is planned for SOFISTv4

\*\* timestamp function is not testable due to mis-match of the readout and sensor wafer types

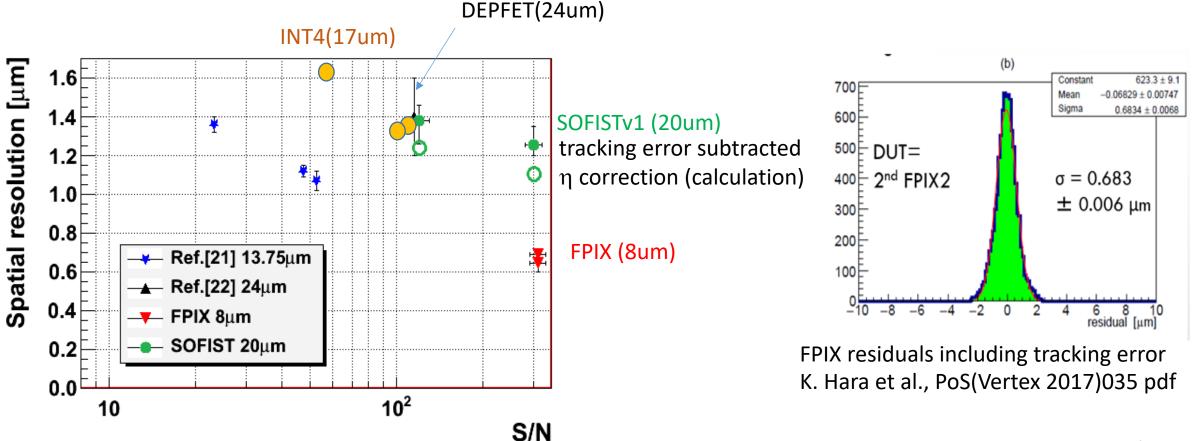

### **SOFIST-v1** spatial resolution

SOFIST residual to FPIX track ( $\sigma$ \_track~0.57/0.65 $\mu$ m) **Bias=130V (~500um depletion) =>15V (~200µm depletion)** 20x20μm pixels **Readout: external 12-b ADCs** =>on-chip 8-b column ADCs SOFIST#2(BPW16x16) SOFIST#1(BPW14x14) plots are for "black case" Residual X: 4 Residual X: 5 h\_resx\_4 h\_resx\_5 Entries 1784 Entries 2401 ₹ 220 <sup>®</sup> 140 0.1503 Mean Mean 0.1677 Std Dev 2.795 Std Dev 200 2.72  $\chi^2$  / ndf 12.1/9  $\gamma^2$  / ndf 12.58 / 9 Constant 139.5 ± 5.8 Constant 227.7 ± 7.6 0.2746 ± 0.0553 Mean Mean 0.1668 ± 0.0386 **Residual X** Sigma 1.504 ± 0.054 Sigma 1.367 ± 0.035  $1.50 \pm 0.05 \,\mu m$  $1.37 \pm 0.04 \,\mu m$  $1.57 \pm 0.08 \,\mu m$  $1.49 \pm 0.06 \,\mu m$ 40  $1.58 \pm 0.05 \,\mu m$  $1.33 \pm 0.03 \,\mu m$ 20 10 1 Residual X [um] Residual X [um] Residual Y: 4 Residual Y: 5 h resy 4 h resy 5 ഇ 240 1784 Entries Entries 2401 ₫ 220 0.01972 -0 1204 Mean Mean 140 Std Dev 2.825 Std Dev 2.694 200  $\chi^2$  / ndf  $\gamma^2$  / ndf 11.4/9 16.79/9  $148.5 \pm 6.4$ Constant Constan 231.2 + 7.90.1282 ± 0.0481 0.06111 ± 0.03750 Mean Mean **Residual Y** 1.378 ± 0.048 1.348 ± 0.035 Sigma Siama  $1.35 \pm 0.04 \,\mu m$  $1.38 \pm 0.05 \,\mu m$  $1.38 \pm 0.05 \,\mu m$  $1.55 \pm 0.08 \,\mu m$ S/N~300 (130V)  $1.54 \pm 0.04 \,\mu m$  $1.32 \pm 0.03 \,\mu m$ ~120 (15V) -10 5 10 Residual Y [um] Residual Y [um]

# **Sensors with O(1um) spatial resolutions**

Spatial resolution improves with S/N as charge-weighted mean position calculation Mostly SOI sensors in this competition World record is 0.65µm achieved by FPIX 8um

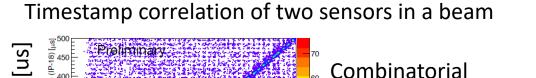

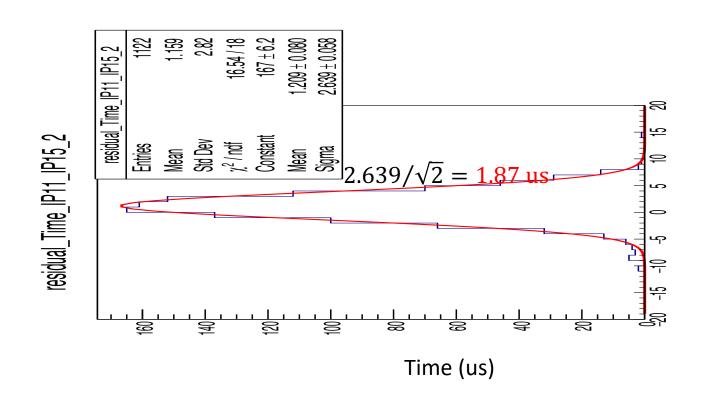

# 25x25µm pixels SOFIST-2 Time stamp resolution

#### SOFISTv2 for timing study thinned to 75 um

Test input

Intrinsic resolution:  $2.19/\sqrt{2} \sim 1.55 \,\mu s$

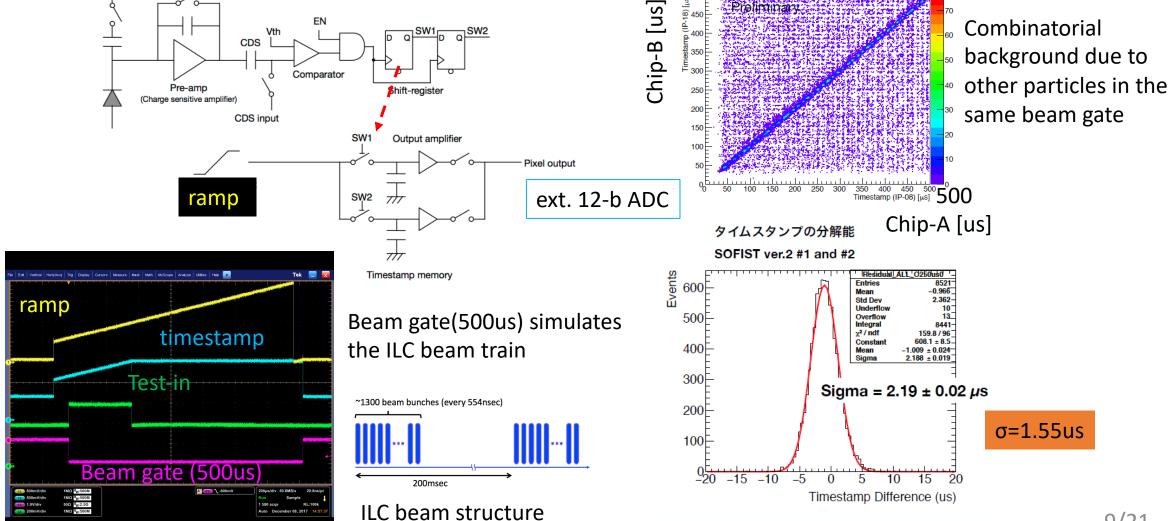

### **SOFIST-2 zero-suppression logic**

Hit map: SOFIST2 200 150 100 50 full scan Hit map: SOFIST2 150

Response to  $\beta$ -ray (time data)

Zero-suppr. (whites are not R/O)

Digitised column data are examined and only hit pixels are stored in FIFO Total scan time= AD conv. ~5 us/colmn(64) x columns(64)~320us vs 340us measured @25MHz clock

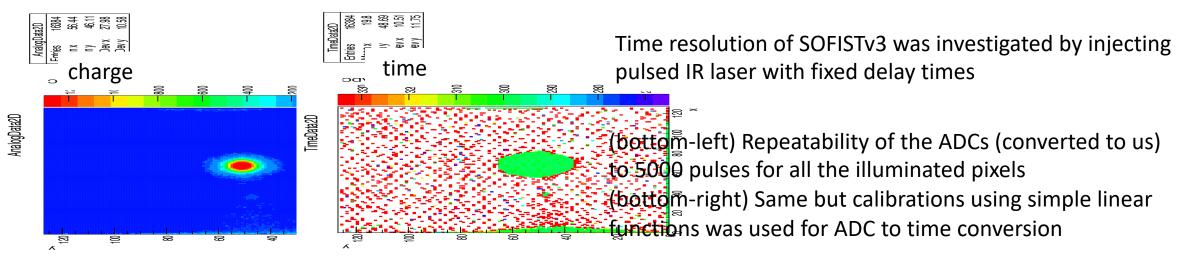

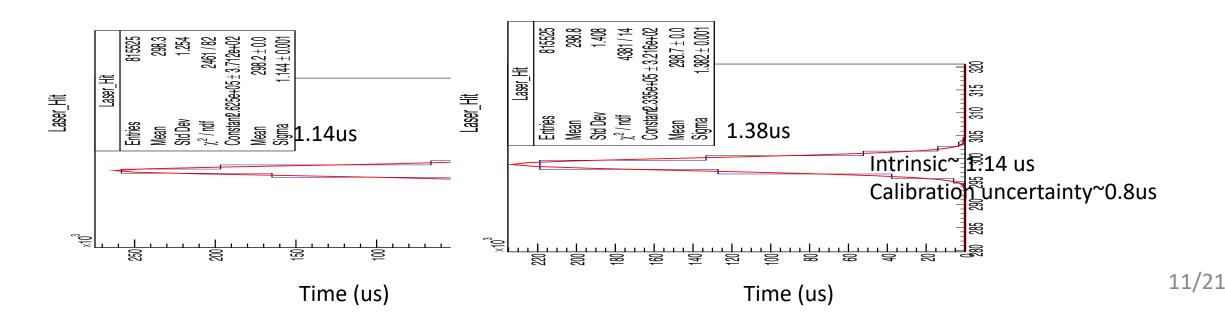

### **SOFIST-3: time resolution w/ laser**

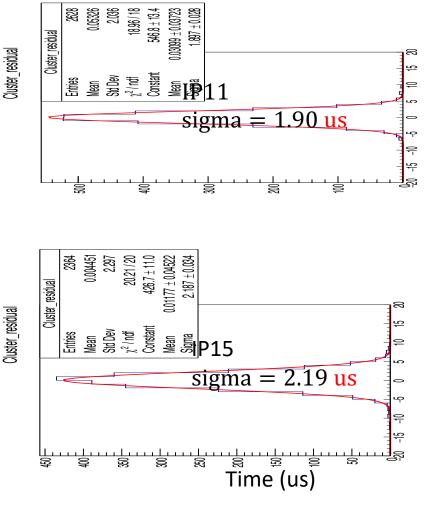

### **SOFIST-3: time resolution in TB**

Time resolution of SOFISTv3 evaluated from time difference of two sensors

Time resolution <2us is demonstrated from test beam data

2hit clusters: time difference

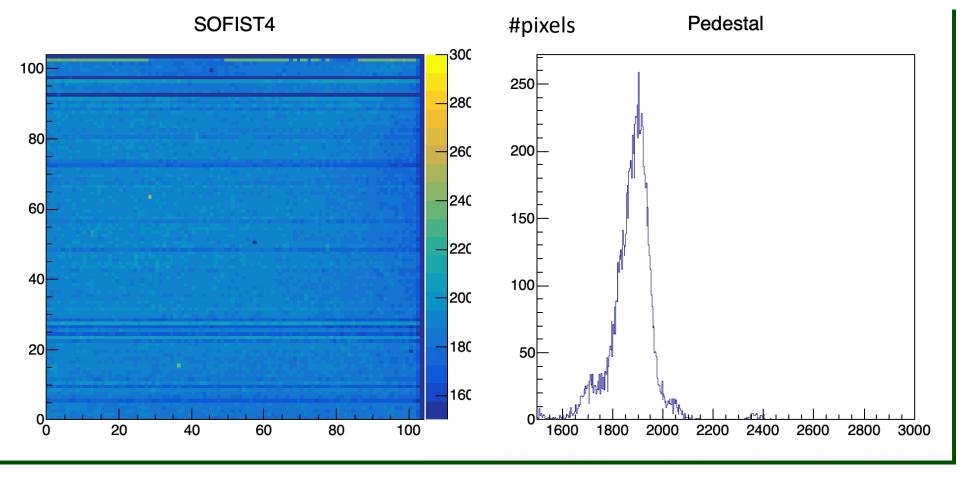

# SOFIST-4: 1<sup>st</sup> 3D stacked SOIPIX sensor

Beam-tested and under final evaluation

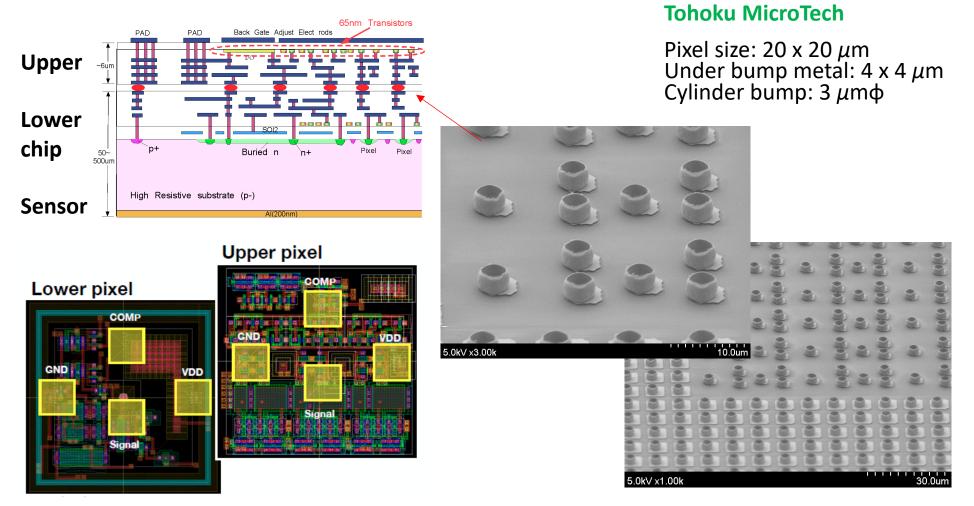

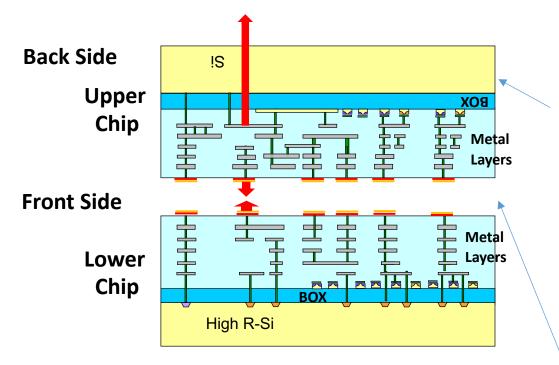

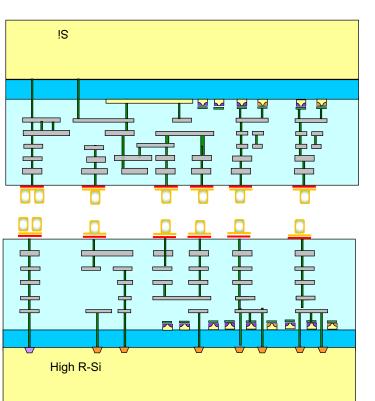

# **SOFIST-4 3D stacking**

#### 3D stacking of SOI chips (chip-on-chip)

→Electronics circuits in two chips are fused using cylindrical microbumps to extend the circuit functionality in limited space

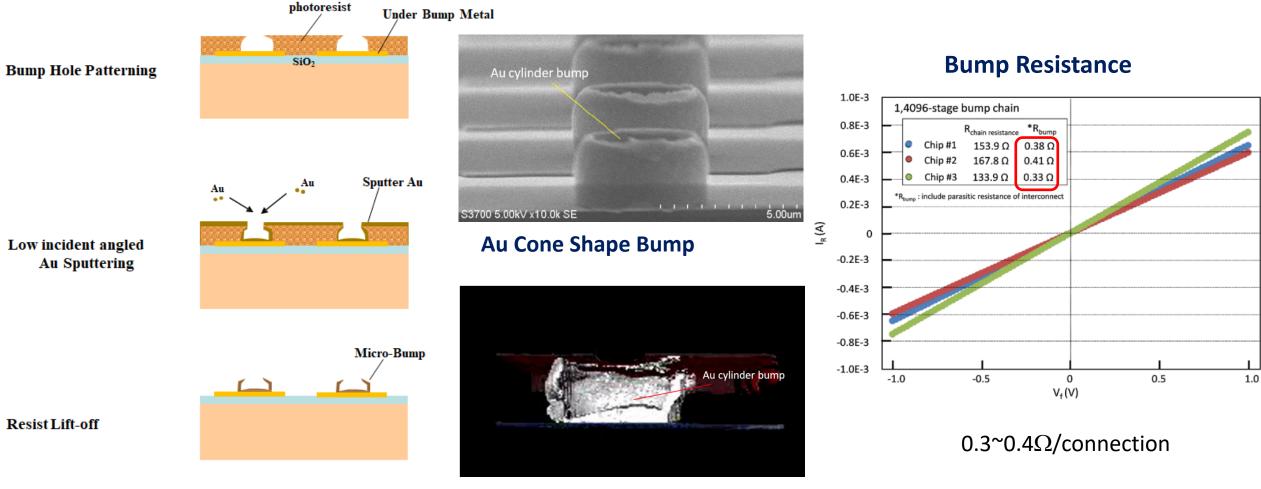

### **Process flow of Au cylindrical bump**

#### **Key Technology : inverse-tapered photoresist**

#### & low incident-angle Au sputtering

Processed by T-Micro

**Cross section of junction**

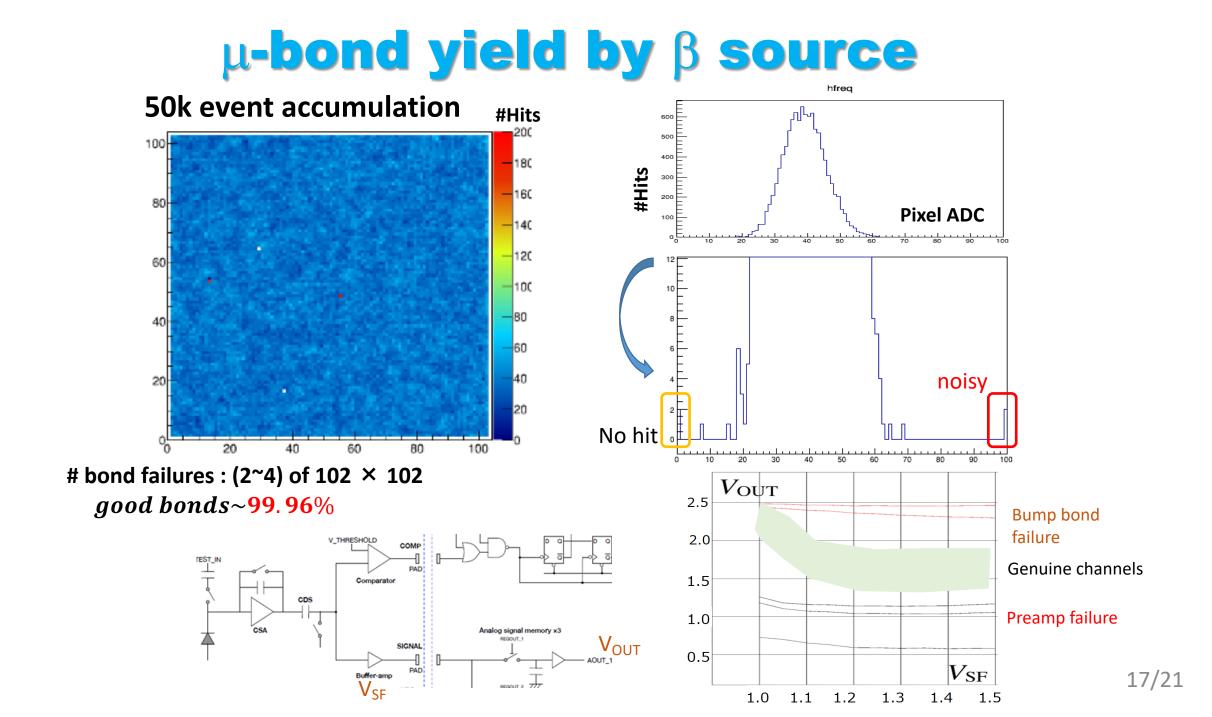

### Response to $\beta$ source

ADC

# **Concepts for chip-on-chip connections**

#### In the case of SOI chips ...

Note: Renesas' 65 nm TB-SOI and ST's 28 nm TB-SOI also utilize "through BOX via" technology

Etch down Si and pads are placed for WB: Relatively thick (150-200nm) BOX of Lapis helps terminate etching as required

Inject epoxy for reinforcement Typical concepts for electrical connections between front and back sides

#### **Back Side**

Through Silicon Via (TSV) size ~5 μm, complicated Through BOX Via (TBV) Our

size ~0.3 µm, simple technology

#### **Front Side**

Cu-Cu direct bonding (SAB) require quite flat surface µ-Bump Cu/Ni/SnAg In Au (cone, cylinder)

oxidation-resistant metal

### **Advantages of SOI micro-bump bonding**

- Requirement on the surface flatness is moderate, as the height of the cylinders can be self adjusted by deformation: a few μm tolerance.

cf. Cu-on-CU 3D

- Soft cylindrical gold bumps result in high-connection yield, as shown.

- No TSV , but Through BOX via (TVB) are processed in the SOI CMOS circuit processes. Fine TVB (0.3um) can be fabricated.. cf. TSV 3D

- Relatively thick BOX (150-200nm) easies top silicon removal etching process

- Upper chip: Only CMOS circuit below SiO<sub>2</sub> remains.

- The remaining thickness is about 8  $\mu\text{m}.$

- Circuit chip has SiO<sub>2</sub> layers on both sides: stacking can be further repeated

SOI and 3D are in very good compatibility

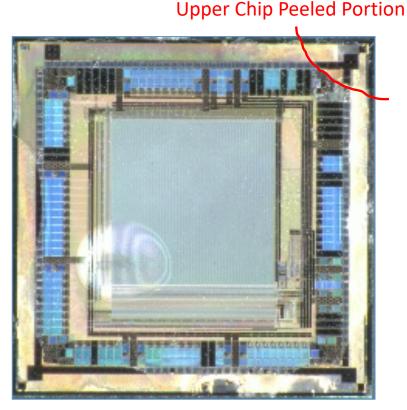

# **Rad-hardness of adhesive glue**

Proton irradiation : 400 kGy ( $5 \times 10^{14}$  cm<sup>-2</sup> in 1 MeV neutron equivalent)

Before irradiation

After irradiation

#### No obvious damage was observed

#### even though the dose level is threshold to create Si displacement defects.

An test chip from process condition tuning was evaluated. The upper chip had some peeled edges but still good enough to evaluate glue damage.

- Color difference is due to lighting

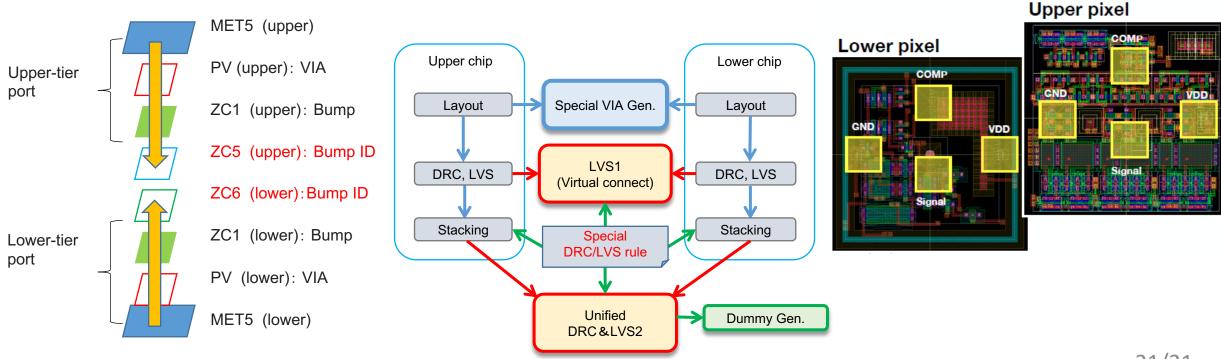

# **3D design tool**

- *Virtuoso* with dedicated rule files.

- Virtual layers are automatically generated between upper and lower chips that unify the chips geometrically and logically.

- *DRC* (design rule check) and *LVS* (layout versus schematic) can be applied for the whole pixel system.

#### 3D can be designed as for conventional SOI

- In the past 7 years, we have been developing SOFIST for the ILC vertex tracker

- Excellent performance has been demonstrated on the spatial and timestamp resolutions, verifying superiority of SOFIST as a deadtime-less device recording timestamp at O(1us) precision over the ILC train duration. Column ADCs, sensor thinning to 50um have also been verified.

- 3D stacking allows to keep the pixel size small (20x20um). SOI is in very good compatibility to the 3D stacking.

However, to adopt SOFIST to the ILC vertex

- Power consumption needs to be lowered. As the demonstrated detector performance is well within the requirements, compromise of the preamplifier speed (hence power) is foreseen.

- Periphery circuits to analog power-off in between trains, to transfer digitized data, and etc., with micro-channel cooling incorporated are to be investigated.

- have a full size chip

#### Acknowledgements:

JSPS Grant-in-Aid for Scientific Research on Innovative Areas (No. 25109006) 2013-2017 Japan/US Cooperation Program in the Field of High Energy Physics 2016, 2018-2019 FTBF- FNAL test beam facility CYRIC (Tohoku U) for proton irradiation

VDEC (U Tokyo) in collaboration with Synopsys, Inc., Cadence Design Systems, Inc., and Mentor Graphics, Inc.

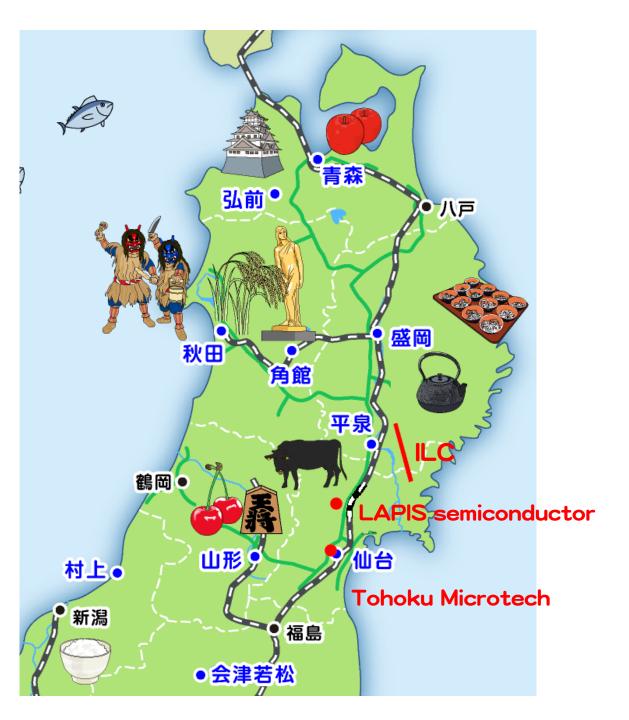

Lapis is the closest foundry to ILC T-Micro is in Sendai Proton irradiation at Tohoku U

https://mapandnews-japan.com/mapsearch\_touhoku.html

### **Power dissipation**

Current SOFIST: preamp + NMOS SFs: (2.75 uA) x 64 x 64 pixels x 1.8 V ~ 13mW  $\Rightarrow$  0.86W/full chip $\Rightarrow$  126W/146chips or 138mW/cm<sup>2</sup>

We started investigating ALPIDE type low power preamp\*

| *Comparison of preamp characteristics |                 |                 |  |  |  |  |

|---------------------------------------|-----------------|-----------------|--|--|--|--|

| Parameters                            | SOFIST          | ALPIDE for SOI* |  |  |  |  |

| Preamp Gain                           | 40 μV/e-        | ~4 mV/e-        |  |  |  |  |

| Sensor capacitance                    | 34 fF           | 3 fF            |  |  |  |  |

| Pixel power                           | 2.75 μA/cell    | 80 nA/cell      |  |  |  |  |

|                                       | *50um depletion | *i_reset 0.2nA  |  |  |  |  |

From TDR

CMOS 600W⇒10W by 2% duty cycle – air cooling

FPCCD 35W inside the cryostat (50um CFRP sheets) – two-phase CO2 cooling

DEPFET – air cooling

For 10W for the entire barrel ( $S^{1600cm^2}$ )  $\Rightarrow$  6.3mW/cm<sup>2</sup> ?

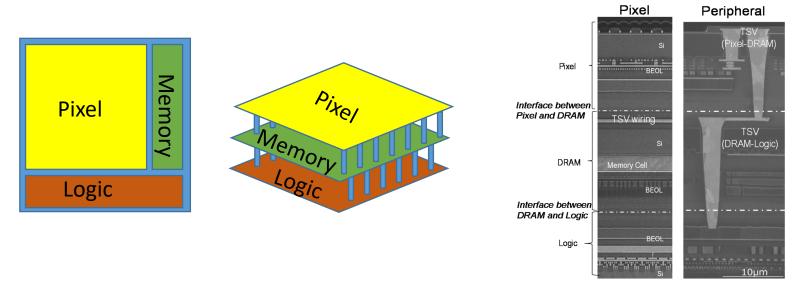

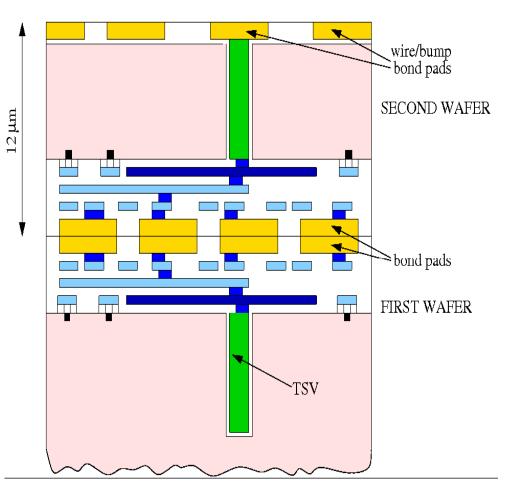

# 3D stacking (1) TSV

For the commercial image sensors, the first trial is to move the peripheral circuits to the second chip and stacked by using TSV, through silicon via.

- This is not an answer for HEP. We have to increase the performance of circuit in each pixel. Pixel-by-pixel connection is necessary.

- Parallel data processing.

- Low power operation thanks to minimum parasitic capacitance.

### 3D stacking methods (2) Direct Bonding Interconnect

- Two wafers are prepared.

- The bonding surface is flattened and cleaned.

- Aligned and attached. Apply suitable pressure and heat for the diffusion bonding of pads.

- SiO2 surfaces is also fused, resulting in the stable structure.

- Widely used for the mass production of high-end image sensors.

From the slide of Valerio Re, Vertex2018